Konvencionalna elektronika zasnovana na silicijumu približava se svojim granicama u pogledu performansi i skalabilnosti. Poslednjih godina, inženjeri su na taj način pokušavali da uvedu alternativne dizajne koji bi mogli da pomognu u smanjenju veličine elektronskih komponenti, a istovremeno poboljšaju njihovu brzinu i energetsku efikasnost.

Istraživači sa Univerziteta Kalifornije u Santa Barbari osmislili su novi okvir koji bi mogao da doprinese ovoj potrazi, omogućavajući proizvodnju skalabilnih trodimenzionalnih (3D) tranzistora sa efektom polja (FET) zasnovanih na dvodimenzionalnim (2D) slojevitim poluprovodnicima. Njihov predloženi pristup, naveden u Nature Electronics, uzima u obzir ključne faktore koji mogu uticati na performanse ovih tranzistora, uključujući takozvane efekte Šotkijevog kontakta i inkluzivnu kapacitivnost.

„Naša istraživačka grupa je bila među prvim saradnicima koji su naglasili važnost arhitekture sa više kapija za postizanje realističnih FET-ova ispod 10 nm, čak i sa atomski tankim kanalima zasnovanim na 2D poluprovodnicima“, rekao je Kaustav Banerjee, stariji autor rada, u intervjuu za Tech Ksplore.

„Ova perspektiva je dalje istražena u našem nedavnom radu na budućim tranzistorima, gde smo sarađivali sa vodećim stručnjacima iz industrije poluprovodnika kako bismo istakli potencijal trodimenzionalnih tranzistora.

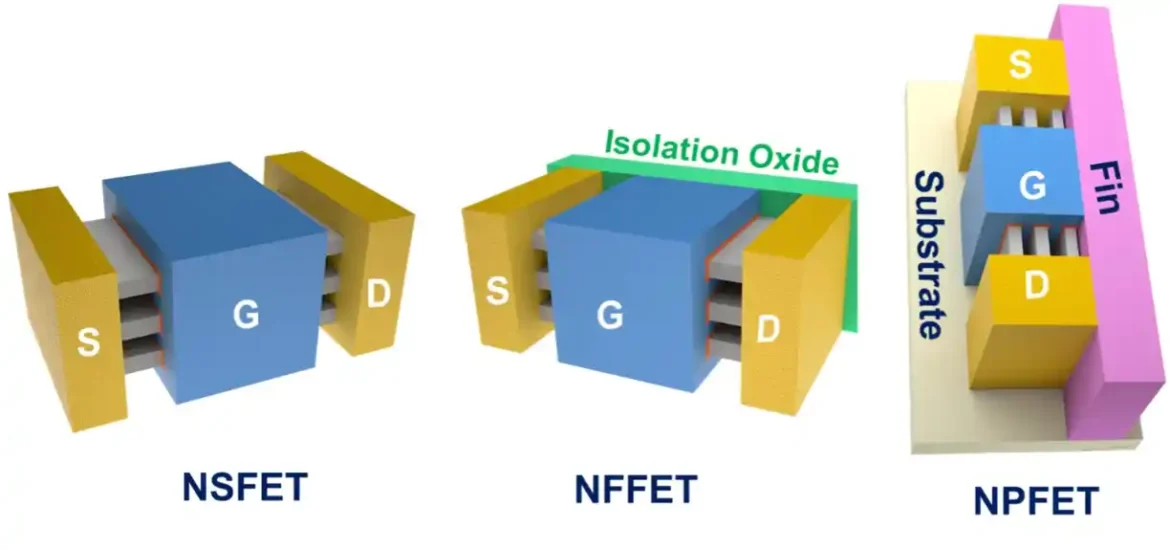

Glavni cilj nedavnog rada Banerjee-a i njegovih kolega bio je da pokažu potencijal atomski tankih 2D slojevitih materijala za proizvodnju 3D-FET-a sledeće generacije sa različitim arhitekturama. Pored toga, istraživači su se nadali da će steći uvid u to koji materijal, arhitektura i dizajn su optimalni za ove tranzistore.

Dok su sprovodili svoju studiju, otkrili su da se 2D materijali takođe mogu jedinstveno konstruisati da bi se stvorila potpuno nova tranzistorska arhitektura, koju su nazvali nano-plate FET (NPFET). Ova arhitektura bi mogla da pokaže poboljšane performanse i veću gustinu integracije.

„Naš predloženi okvir za projektovanje skaliranih 3D tranzistora uključuje korišćenje formalizma kvantnog transporta za simulaciju transporta nosioca, koristeći komercijalno dostupan alat za kompjuterski potpomognuto projektovanje (TCAD) koji se zove KTKS“, objasnio je Banerdži. „Ovaj alat koristi neravnotežni Greenov funkcionalni okvir (NEGF), jedan od najmoćnijih pristupa kvantnom transportu.“

Za različite varijante NEGF funkcije, istraživači su koristili efikasan pristup zasnovan na masi. Utvrđeno je da je ova metoda računarski efikasna i tačna, a istovremeno uzima u obzir efekte neparaboličnosti energetskog opsega, satelitske doline i konačnu energetsku širinu ovih dolina.

„Ovi ulazni parametri su izračunati simulacijama teorije funkcionalne gustine (DFT), ab-initio metodom, a zatim uvezeni u KTKS“, rekao je Banerjee. „Takođe smo razmotrili efekat neidealnog otpora kontakta i mobilnosti nosača da bismo sproveli temeljnije simulacije.“

Rezultati simulacija koje su izvršili istraživači sugerišu da 3D-FET-ovi zasnovani na 2D poluprovodnicima mogu postići superiorne performanse u poređenju sa FET-ovima zasnovanim na silicijumu. Dužina kanala ovih 3D-FET-ova zasnovanih na 2D materijalu smanjena je na oko ili ispod 7 nm, a materijal koji je dao najveće dobitke bio je VS 2 .

„Povećana struja pogona, zajedno sa smanjenom kapacitivnošću uređaja zbog tankosti 2D poluprovodnika u poređenju sa silicijumom, poboljšava ukupni proizvod kašnjenja energije (EDP) kola dizajniranih sa 2D tranzistorima zasnovanim na poluprovodnicima“, rekao je Banerdži. „Pored toga, obezbedili smo sveobuhvatan nacrt za projektovanje 3D-FET-ova zasnovanih na 2D poluprovodnicima koji podržavaju buduće CMOS skaliranje.“

Za skaliranje tranzistora, nova NPFET arhitektura koju je uveo ovaj istraživački tim koristi tankoću i vertikalno slaganje 2D poluprovodnika. U poređenju sa uporedivim 3D-FET arhitekturama predstavljenim u prethodnim studijama, ova arhitektura bi mogla da ponudi važne prednosti u pogledu gustine integracije i performansi.

„Naši budući istraživački napori će se fokusirati na blisku saradnju sa industrijskim partnerima kako bismo ubrzali integraciju ovih materijala i dizajna u glavne CMOS procese“, dodao je Banerdži. „Pored toga, cilj nam je da poboljšamo naše simulacije tako što ćemo uključiti širi spektar neidealnih efekata, kao što su rasejanje defekata i samozagrevanje. Ovo će pružiti dublji uvid i podršku eksperimentalnim istraživačima na terenu.“