Decenijama, inženjeri elektronike pokušavaju da razviju sve naprednije uređaje koji mogu brže da obavljaju složene proračune i troše manje energije. Ovo je postalo još izraženije nakon pojave veštačke inteligencije (AI) i algoritama dubokog učenja, koji obično imaju značajne zahteve i u pogledu skladištenja podataka i računarskog opterećenja.

Pristup koji obećava za pokretanje ovih algoritama poznat je kao analogno računanje u memoriji (AIMC). Kao što mu ime sugeriše, ovaj pristup se sastoji od razvoja elektronike koja može da izvodi proračune i čuva podatke na jednom čipu. Da bi se realno postigla poboljšanja u brzini i potrošnji energije, ovaj pristup bi idealno trebalo da podrži i digitalne operacije i komunikacije na čipu.

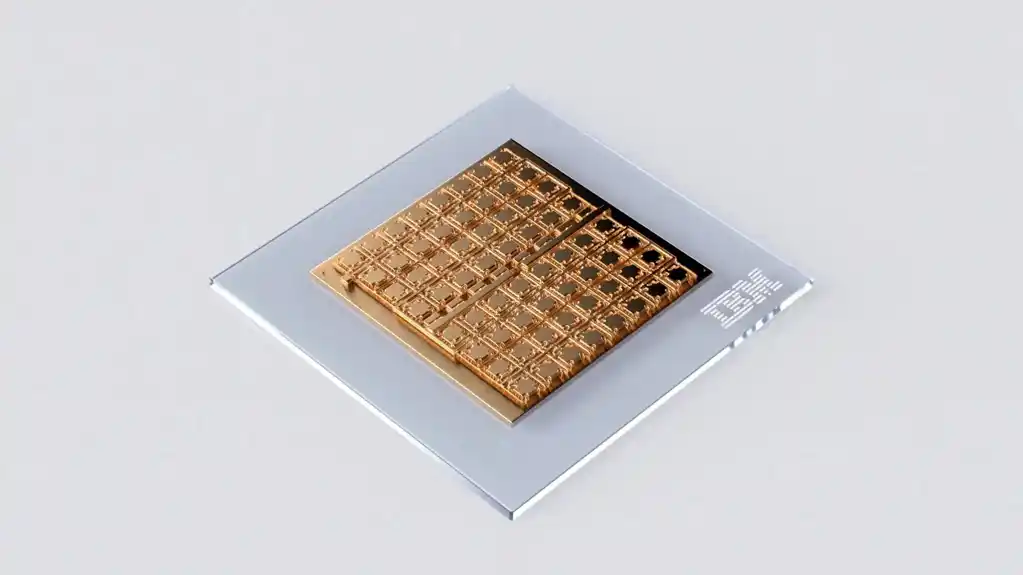

Istraživači iz IBM Research Europe nedavno su razvili novi 64-jezgarni računarski čip sa mešovitim signalom u memoriji zasnovan na memorijskim uređajima sa promenom faze koji bi mogli bolje da podrže proračune dubokih neuronskih mreža. Njihov 64-jezgarni čip, predstavljen u radu u Nature Electronics, do sada je postigao veoma obećavajuće rezultate, zadržavajući tačnost algoritama dubokog učenja, uz smanjenje vremena računanja i potrošnje energije.

„Istraživali smo kako da koristimo memorijske uređaje sa promenom faze (PCM) za računarstvo više od 7 godina, počevši od kada smo prvi put pokazali kako da implementiramo neuronske funkcije sa pojedinačnim PCM uređajima“, rekao je Manuel Le Gallo, jedan od autora novine, rekao je Tech Ksplore.

„Od tada smo pokazali da bi mnoge aplikacije mogle imati koristi od korišćenja PCM uređaja kao računarskih elemenata, kao što su naučno računarstvo i duboko zaključivanje neuronskih mreža, za koje smo pokazali mali ili nikakav gubitak tačnosti u implementaciji hardvera/softvera korišćenjem prototipnih PCM čipova. ovim novim čipom, želeli smo da napravimo korak napred ka analognom AI akceleratorskom čipu od kraja do kraja.“

Da bi kreirali svoj novi računarski čip u memoriji, Le Gallo i njegove kolege su kombinovali jezgra zasnovana na PCM-u sa digitalnim računarskim procesorima, povezujući sva jezgra i jedinice za digitalnu obradu preko digitalne komunikacione mreže na čipu. Njihov čip se sastoji od 64 analogna jezgra zasnovana na PCM-u, od kojih svako sadrži niz sinaptičkih jediničnih ćelija veličine 256 puta 256.

„Integrisali smo kompaktne analogno-digitalne pretvarače zasnovane na vremenu u svako jezgro da bismo prešli između analognog i digitalnog sveta“, objasnio je Le Galo. „Svako jezgro je takođe integrisano sa lakim digitalnim procesorskim jedinicama koje obavljaju funkcije aktivacije neurona rektifikovane linearne jedinice (reLU) i operacije skaliranja. Globalna digitalna procesorska jedinica je integrisana u sredini čipa koja implementira mrežu dugotrajne memorije (LSTM). operacije“.

Jedinstvena karakteristika timskog čipa je da su memorijska jezgra sadržana u njemu i njegova globalna procesorska jedinica povezani preko digitalne komunikacione mreže. Ovo mu omogućava da izvrši sve proračune povezane sa pojedinačnim slojevima neuronske mreže na čipu, značajno smanjujući vreme računanja i potrošnju energije.

Da bi procenili svoj čip, Le Gallo i njegove kolege su sproveli veoma sveobuhvatnu studiju, pokrenuvši algoritme dubokog učenja na svom čipu i testirajući njegove performanse. Rezultati njihove procene su bili izuzetno obećavajući, jer kada su radili na čipu i testirani na skupu podataka slika CIFAR-10, duboke neuronske mreže obučene da završe zadatke prepoznavanja slika postigle su izuzetnu preciznost od 92,81%.

„Verujemo da je ovo najviši nivo tačnosti od svih trenutno prijavljenih čipova koji koriste sličnu tehnologiju“, rekao je Le Galo. „U radu smo takođe pokazali kako možemo neprimetno da kombinujemo analogno računarstvo u memoriji sa nekoliko digitalnih procesorskih jedinica i digitalnim komunikacionim tkivom. Izmerena propusnost po oblasti za 8-bitna množenja ulazno-izlazne matrice od 400 GOPS/mm 2 čip je više od 15 puta veći od prethodnih višejezgarnih računarskih čipova u memoriji zasnovanih na otpornoj memoriji, dok postiže uporedivu energetsku efikasnost.“

Nedavni rad IBM Research Europe je dalji korak ka razvoju AIMC čipova koji mogu da podrže potrebe i zahteve algoritama dubokog učenja. U budućnosti, dizajn koji su predstavili Le Gallo i njegove kolege mogao bi biti dodatno ažuriran kako bi omogućio još bolje performanse.

„Koristeći naše učenje od ovog čipa i drugog čipa od 34 pločice koji je predstavljen na VLSI 2021. godine, dizajnirali smo end-to-end analognu arhitekturu AI zaključivanja koja je objavljena ranije ove godine u IEEE Transactions on VLSI sistemima“, Le dodao je Gallo. „Naša vizija kombinuje mnoge analogne računarske pločice u memoriji sa mešavinom namenskih, digitalnih računarskih jezgara povezanih sa masivno-paralelnom 2D mrežom. U vezi sa sofisticiranom obukom o hardveru koju smo razvili poslednjih godina, očekujemo ove akceleratori za isporuku softverski ekvivalentne tačnosti neuronske mreže u širokom spektru modela u godinama koje dolaze.“